# Audio Codec with Embedded SigmaDSP Processor

# ADAV400

#### FEATURES

Fully programmable audio digital signal processing (DSP) for enhanced sound processing Scalable digital audio delay line Pool of 400 ms @ 48 kHz (200 ms for stereo channel) High performance, integrated analog-to-digital converters (ADCs) and digital-to-analog converters (DACs) 1 stereo analog input (ADC) 4 stereo analog inputs with mux-to-stereo ADC 4 stereo (8-channel) analog outputs (DACs) Dedicated headphone output with integrated amplifier Multichannel digital I/O 8-channel I<sup>2</sup>S input and output modes 8- and 16-channel TDM input and output modes 2-channel (1 stereo) asynchronous I<sup>2</sup>S input with integrated sample rate converter (SRC), supporting sample rates from 5 kHz to 50 kHz

Features SigmaStudio™, a proprietary graphical programming tool for fast development of custom signal flows Includes various third-party audio algorithms

I<sup>2</sup>C control interface

Operates from 3.3 V (analog), 1.8 V (digital core), 3.3 V (digital interface)

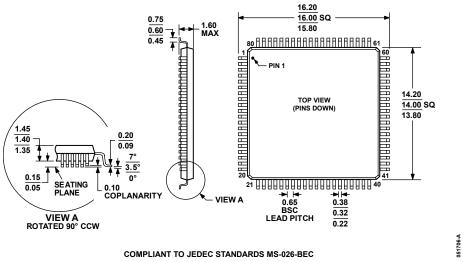

Features on-chip regulator for single 3.3 V operation 80-lead LQFP (14 mm × 14 mm)

Temperature range: 0°C to 70°C

#### APPLICATIONS

ATV and AV audio applications TV audio processing Set-top box (STB) HTiB General audio enhancement

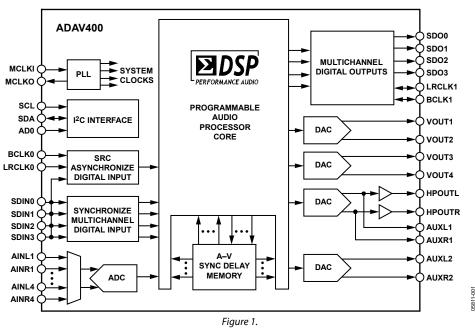

#### FUNCTIONAL BLOCK DIAGRAM

Rev. A Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| Functional Block Diagram1                    |

| Revision History                             |

| General Description                          |

| Specifications                               |

| Digital Timing6                              |

| Absolute Maximum Ratings                     |

| ESD Caution                                  |

| Pin Configuration and Function Descriptions9 |

| Typical Performance Characteristics          |

| Theory of Operation                          |

| Analog Inputs13                              |

| Sample Rate Converter Block                  |

| PLL Block13                                  |

| Analog Outputs13                             |

| Headphone Amplifier14                        |

| Voltage Regulator                            |

| Control Port 15                              |

| I <sup>2</sup> C Port                        |

| Signal Processing                            |

| Numeric Formats                              |

| Programming18                                |

### **REVISION HISTORY**

| 7/07—Rev. 0 to Rev. A                                     |

|-----------------------------------------------------------|

| Change to ADC Section, Total Harmonic Distortion + Noise4 |

| Change to DAC Outputs (Single-Ended),                     |

| Total Harmonic Distortion + Noise                         |

| Changes to Ordering Guide                                 |

1/06—Revision 0: Initial Version

| RAMs and Registers19                                |

|-----------------------------------------------------|

| Control Port Addressing 19                          |

| Parameter RAM Contents19                            |

| Recommended Program/Parameter Loading Procedures 20 |

| Target/Slew RAM 20                                  |

| Safe Load Registers                                 |

| Data Capture Registers                              |

| Control Port Read/Write Data Formats                |

| Serial Data Input/Output Ports                      |

| Control Registers                                   |

| Audio Core Control Register 31                      |

| RAM Modulo Control Register                         |

| Serial Output Control Registers                     |

| Serial Input Control Register 32                    |

| SRC Serial Port Control Register                    |

| ADC Input Mux Register                              |

| Power Control Register                              |

| User Control Register 2 33                          |

| User Control Register 1 33                          |

| DAC Amplifier Register                              |

| Typical Application Diagram                         |

| Outline Dimensions                                  |

| Ordering Guide                                      |

## **GENERAL DESCRIPTION**

The ADAV400 is an enhanced audio processor. Integrating high performance analog and digital I/Os with a powerful, audiospecific, programmable core enables designers to differentiate their products through audio performance.

The audio processing core is based on Analog Devices SigmaDSP<sup>\*</sup> technology featuring full 28-bit processing (56-bit in double precision mode); a sophisticated, fully programmable dynamics processor; and delay memory.

This technology allows the system designer to compensate for real-world limitations of speakers, amplifiers, and listening environments. This compensation results in a dramatic improvement of the perceived audio quality through speaker equalization, multiband compression and limiting, and thirdparty-branded algorithms.

The analog I/O integrates Analog Devices proprietary continuous time, multibit, sigma-delta  $(\Sigma - \Delta)$  architecture. This integration

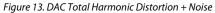

brings a higher level of performance to systems that are required to meet system branding certification by third-party algorithm providers. The analog inputs feature a 95 dB dynamic range stereo ADC fed from a four-stereo input mux. The four stereo analog outputs are each driven by a 95 dB dynamic range DAC. A dedicated headphone channel is included with integrated amplifiers.

The ADAV400 supports multichannel digital inputs and outputs. An integrated SRC on one channel provides the capability to support any input sample rate in the range of 5 kHz to 50 kHz, synchronizing this input to the internal DSP engine.

The ADAV400 is supported by a powerful graphical programming tool that includes blocks such as general filters, EQ filters, dynamics processing, mixers, volume, and third-party algorithms for fast development of custom signal flows.

# SPECIFICATIONS

$AVDDn^1 = 3.3 V$ , ODVDD = 3.3 V, DVDD = internal voltage regulator, temperature = 0°C to 70°C, master clock = 12.288 MHz, measurement bandwidth = 20 Hz to 20 kHz, ADC input signal = 1 kHz, DAC output signal = 1 kHz, unless otherwise noted.

| Table 1.                                                                  | A.4. | <b>T</b>       |     | 11 **              |                                                                      |

|---------------------------------------------------------------------------|------|----------------|-----|--------------------|----------------------------------------------------------------------|

| Parameter                                                                 | Min  | Тур            | Max | Unit               | Test Conditions/Comments                                             |

| REFERENCE SECTION                                                         |      |                |     |                    |                                                                      |

| Absolute Voltage (V <sub>REF</sub> )                                      |      | 1.5            |     | V                  |                                                                      |

| V <sub>REF</sub> Temperature Coefficient                                  |      | 130            |     | ppm/°C             |                                                                      |

| ANALOG INPUTS (SINGLE ENDED)                                              |      |                |     |                    |                                                                      |

| Number of Channels                                                        |      | 8              |     |                    | Four stereo input channels                                           |

| Full-Scale Analog Input                                                   |      | 100            |     | μA rms             | 2 V rms input with 20 k $\Omega$ series resistor                     |

| DC Offset                                                                 |      | ±10            |     | mV                 | Relative to V <sub>REF</sub>                                         |

| ADC SECTION                                                               |      |                |     |                    | Stereo ADC                                                           |

| Resolution                                                                |      | 24             |     | Bits               |                                                                      |

| Dynamic Range                                                             |      |                |     |                    |                                                                      |

| A-Weighted                                                                | 90   | 95             |     | dB                 | –60 dB with respect to full-scale analog input                       |

| Total Harmonic Distortion + Noise                                         |      | -90            |     | dB                 | –3 dB with respect to full-scale analog input                        |

| Interchannel Gain Mismatch                                                |      | 0.1            |     | dB                 | Left and right channel gain mismatch                                 |

| Crosstalk                                                                 |      | -78            |     | dB                 | Analog channel crosstalk (AINYm <sup>2</sup> to AINYm <sup>2</sup> ) |

|                                                                           |      |                |     |                    | One channel = $-3$ dB, other channel = $0$ V                         |

| Gain Error                                                                |      | -6             |     | %                  |                                                                      |

| Power Supply Rejection                                                    |      | -83            |     | dB                 | 1 kHz, 300 mV p-p signal at AVDDn <sup>1</sup>                       |

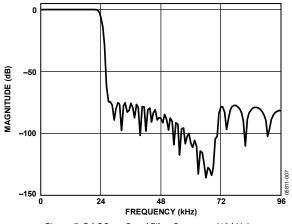

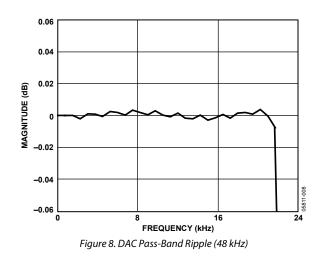

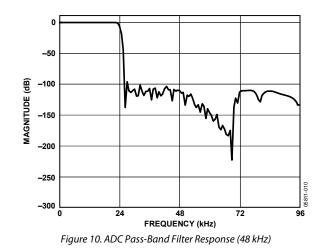

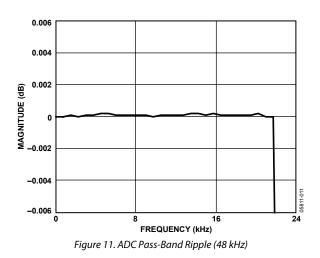

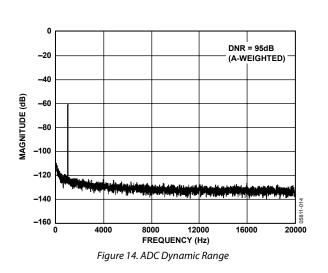

| ADC DIGITAL DECIMATOR FILTER<br>CHARACTERISTICS @ 48 kHz <sup>3</sup>     |      |                |     |                    |                                                                      |

| Pass Band                                                                 |      | 22.5           |     | kHz                |                                                                      |

| Pass-Band Ripple                                                          |      | ±0.0002        | 2   | dB                 |                                                                      |

| Transition Band                                                           |      | 24             |     | kHz                |                                                                      |

| Stop Band                                                                 |      | 26.5           |     | kHz                |                                                                      |

| Stop-Band Attenuation                                                     |      | 100            |     | dB                 |                                                                      |

| Group Delay                                                               |      | 1040           |     | μs                 |                                                                      |

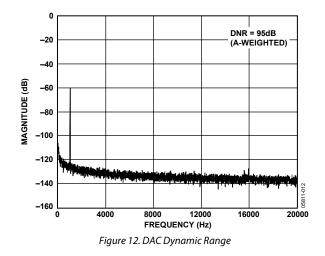

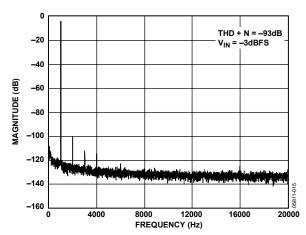

| DAC OUTPUTS (SINGLE-ENDED)                                                |      |                |     |                    | DAC amplifier register contents = 0x0010                             |

| Number of Channels                                                        |      | 8              |     |                    | Four stereo output channels                                          |

| Resolution                                                                |      | 24             |     | Bits               |                                                                      |

| Full-Scale Analog Output                                                  |      | 1              |     | V rms              |                                                                      |

| Dynamic Range                                                             |      |                |     |                    |                                                                      |

| A-Weighted                                                                | 90   | 95             |     | dB                 | –60 dB with respect to full-scale code input                         |

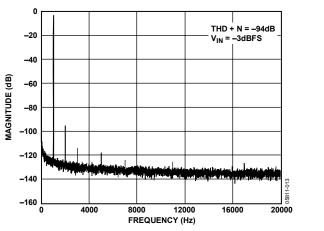

| Total Harmonic Distortion + Noise <sup>4</sup>                            | -    | -93            |     | dB                 | -3 dB with respect to full-scale code input                          |

| Crosstalk                                                                 |      | -100           |     | dB                 | Analog channel crosstalk (VOUTm <sup>2</sup> to VOUTm <sup>2</sup> ) |

|                                                                           |      |                |     |                    | One channel = $-3$ dB, other channels = $0$ V                        |

| Gain Error                                                                |      | 5              |     | %                  |                                                                      |

| Interchannel Gain Mismatch                                                |      | 0.1            |     | dB                 | Left and right channel gain mismatch                                 |

| DC Offset                                                                 |      | 1              |     | mV                 | Relative to V <sub>REF</sub>                                         |

| Power Supply Rejection                                                    |      | -87            |     | dB                 | 1 kHz, 300 mV p-p signal at AVDDn <sup>1</sup>                       |

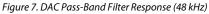

| DAC DIGITAL INTERPOLATION FILTER<br>CHARACTERISTICS @ 48 kHz <sup>3</sup> |      |                |     |                    | ,                                                                    |

| Pass Band                                                                 |      | 21.769         |     | kHz                |                                                                      |

| Pass-Band Ripple                                                          |      | ±0.01          |     | dB                 |                                                                      |

| Transition Band                                                           |      | ±0.01<br>23.95 |     | ив<br>kHz          |                                                                      |

|                                                                           |      |                |     | кн <i>г</i><br>kHz |                                                                      |

| Stop Band                                                                 |      | 26.122         |     |                    |                                                                      |

| Stop-Band Attenuation                                                     |      | 75             |     | dB                 |                                                                      |

| Group Delay                                                               |      | 580            |     | μs                 |                                                                      |

| Parameter                                                        | Min             | Тур  | Max              | Unit  | Test Conditions/Comments                                           |

|------------------------------------------------------------------|-----------------|------|------------------|-------|--------------------------------------------------------------------|

| HEADPHONE OUTPUT (SINGLE ENDED)                                  |                 |      |                  |       | Measured at headphone output with 32 $\Omega$ load,                |

|                                                                  |                 |      |                  |       | headphone amplifier register contents = 0x0001                     |

| Number of Channels                                               |                 | 2    |                  |       | One stereo channel                                                 |

| Resolution                                                       |                 | 24   |                  | Bits  |                                                                    |

| Full-Scale Analog Output                                         |                 | 1    |                  | V rms |                                                                    |

| Dynamic Range                                                    |                 |      |                  |       |                                                                    |

| A-Weighted                                                       |                 | 92   |                  | dB    | -60 dBFS with respect to full-scale code input                     |

| Total Harmonic Distortion + Noise                                |                 | -84  |                  | dB    | -3 dBFS with respect to full-scale code input                      |

| Gain Error                                                       |                 | 4    |                  | %     |                                                                    |

| Interchannel Gain Mismatch                                       |                 | 0.5  |                  | dB    |                                                                    |

| DC Offset                                                        |                 | -30  |                  | mV    | Relative to V <sub>REF</sub>                                       |

| Power Supply Rejection                                           |                 | -84  |                  | dB    | 1 kHz, 300 mV p-p signal at AVDDn <sup>1</sup>                     |

| PLL SECTION <sup>3</sup>                                         | _               |      |                  |       |                                                                    |

| Master Clock Input (MCLKI)                                       | $64 \times f_s$ |      | $512 \times f_s$ | MHz   |                                                                    |

| SRC <sup>3</sup>                                                 |                 |      |                  |       |                                                                    |

| Dynamic Range                                                    |                 |      |                  |       |                                                                    |

| A-Weighted                                                       |                 | 115  |                  | dB    | $-60 \text{ dBFS input (worst-case input, } f_s = 50 \text{ kHz})$ |

| Total Harmonic Distortion + Noise                                |                 | -113 |                  | dB    | 0 dBFS input (worst-case input, f <sub>s</sub> = 50 kHz)           |

| Sample Rate                                                      | 5               |      | 50               | kHz   |                                                                    |

| DIGITAL INPUT/OUTPUT                                             |                 |      |                  |       |                                                                    |

| Input Voltage High (V <sub>IH</sub> )                            | 2.0             |      | ODVDD            | V     |                                                                    |

| Input Voltage Low (V <sub>IL</sub> )                             |                 |      | 0.8              | V     |                                                                    |

| Input Leakage (I <sub>IH</sub> @ V <sub>IH</sub> = ODVDD)        |                 |      | 10               | μΑ    |                                                                    |

| Input Leakage (I <sub>IL</sub> @ V <sub>IL</sub> = 0 V)          | -60             |      |                  | μΑ    |                                                                    |

| Output Voltage High (V <sub>OH</sub> @ l <sub>OH</sub> = 0.4 mA) | 2.4             |      |                  | V     |                                                                    |

| Output Voltage Low ( $V_{OL} @ I_{OL} = -3.2 \text{ mA}$ )       |                 |      | 0.4              | V     |                                                                    |

| Input Capacitance                                                |                 | 10   |                  | pF    |                                                                    |

| SUPPLIES                                                         |                 |      |                  |       |                                                                    |

| Analog Supplies (AVDDn) <sup>1</sup>                             | 3.15            | 3.30 | 3.45             | V     |                                                                    |

| Digital Supplies (DVDD)                                          | 1.6             | 1.8  | 2.0              | V     |                                                                    |

| Interface Supply (ODVDD)                                         | 3.15            | 3.30 | 3.45             | V     |                                                                    |

| Supply Current, Normal Mode                                      |                 |      |                  |       | MCLK = 12.288 MHz, ADCs and DACs active,                           |

| Analog Current (AVDD1)                                           |                 | 90   | 110              | mA    | headphone outputs active and driving a 32 $\Omega$ load,           |

| Digital and Interface Current                                    |                 | 120  | 135              | mA    | Power control register = 0xFFFF                                    |

| PLL Current                                                      |                 | 5    | 6                | mA    |                                                                    |

| Supply Current, Power-Down Mode                                  |                 |      |                  |       | RESET low, MCLK = 3.074 MHz, AINx = AGND, DAC                      |

| Analog Current                                                   |                 | 6    | 8.5              | mA    | and headphone outputs floating                                     |

| Digital and Interface Current                                    |                 | 1.5  | 6                | mA    |                                                                    |

| PLL Current                                                      |                 | 5    | 50               | μA    |                                                                    |

<sup>1</sup> The n refers to supply number.

<sup>2</sup> The m refers to channel number, and the Y refers to stereo channel identifier: L for left channel or R for right channel.

<sup>3</sup> Guaranteed by design.

<sup>4</sup> Measured on one DAC with other DACs and ADCs off.

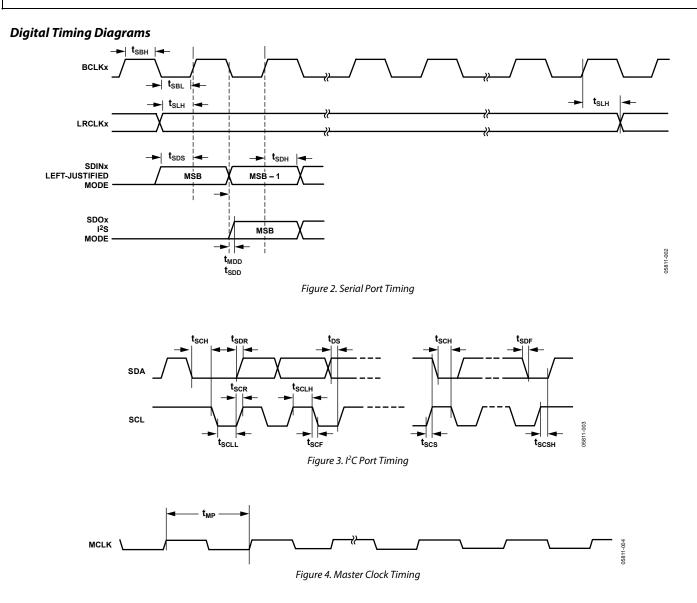

### **DIGITAL TIMING**

#### Table 2.

| Parameter                                 | Min             | Max    | Unit | Comments                                       |

|-------------------------------------------|-----------------|--------|------|------------------------------------------------|

| MASTER CLOCK AND RESET                    |                 |        |      |                                                |

| f <sub>мські</sub> (MCLKI Frequency)      | 3.024           | 24.576 | MHz  |                                                |

| t <sub>MCH</sub> (MCLKI High)             | 10              |        | ns   |                                                |

| t <sub>MCL</sub> (MCLKI Low)              | 10              |        | ns   |                                                |

| t <sub>RLPW</sub> (RESET Low Pulse Width) | 20              |        | ns   |                                                |

| I <sup>2</sup> C <sup>®</sup> PORT        |                 |        |      |                                                |

| f <sub>scl</sub> (SCL Clock Frequency)    |                 | 400    | kHz  |                                                |

| t <sub>SCLH</sub> (SCL High)              | 0.6             |        | μs   |                                                |

| t <sub>SCLL</sub> (SCL Low)               | 1.3             |        | μs   |                                                |

| Start Condition                           |                 |        |      |                                                |

| t <sub>scs</sub> (Setup Time)             | 0.6             |        | μs   | Relevant for repeated start condition          |

| t <sub>scн</sub> (Hold Time)              | 0.6             |        | μs   | The first clock is generated after this period |

| t <sub>DS</sub> (Data Setup Time)         | 100             |        | ns   |                                                |

| t <sub>SCR</sub> (SCL Rise Time)          |                 | 300    | ns   |                                                |

| t <sub>SCF</sub> (SCL Fall Time)          |                 | 300    | ns   |                                                |

| t <sub>sDR</sub> (SDA Rise Time)          |                 | 300    | ns   |                                                |

| t <sub>SDF</sub> (SDA Fall Time)          |                 | 300    | ns   |                                                |

| Stop Condition                            |                 |        |      |                                                |

| t <sub>SCSH</sub> (Setup Time)            | 0.6             |        | μs   |                                                |

| SERIAL PORTS                              |                 |        |      |                                                |

| Slave Mode                                |                 |        |      |                                                |

| t <sub>sвн</sub> (BCLKx High)             | 40              |        | ns   |                                                |

| t <sub>SBL</sub> (BCLKx Low)              | 40              |        | ns   |                                                |

| f <sub>SBF</sub> (BCLKx Frequency)        | $64 \times f_s$ |        |      |                                                |

| t <sub>SLS</sub> (LRCLKx Setup)           | 10              |        | ns   | To BCLK rising edge                            |

| t <sub>SLH</sub> (LRCLKx Hold)            | 10              |        | ns   | From BCLK rising edge                          |

| t <sub>SDS</sub> (SDINx Setup)            | 10              |        | ns   | To BCLK rising edge                            |

| t <sub>SDH</sub> (SDINx Hold)             | 10              |        | ns   | From BCLK rising edge                          |

| t <sub>SDD</sub> (SDOx Delay)             |                 | 40     | ns   | From BCLK falling edge                         |

| Master Mode                               |                 |        |      |                                                |

| t <sub>MLD</sub> (LRCLKx Delay)           |                 | 5      | ns   | From BCLK falling edge                         |

| t <sub>MDD</sub> (SDOx Delay)             |                 | 40     | ns   | From BCLK falling edge                         |

| t <sub>MDS</sub> (SDINx Setup)            | 10              |        | ns   | From BCLK rising edge                          |

| t <sub>MDH</sub> (SDINx Hold)             | 10              |        | ns   | From BCLK rising edge                          |

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Parameter          | Rating                             |

|--------------------|------------------------------------|

| DVDD to DGND       | 0 V to 2.2 V                       |

| ODVDD to DGND      | 0 V to 4.0 V                       |

| AVDD to AGND       | 0 V to 4.0 V                       |

| AGND to DGND       | –0.3 V to +0.3 V                   |

| Digital Inputs     | DGND – 0.3 V to ODVDD + 0.3 V      |

| Analog Inputs      | AGND – 0.3 V to ADVDD + 0.3 V      |

| Reference Voltage  | Indefinite short circuit to ground |

| Soldering (10 sec) | 300°C                              |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

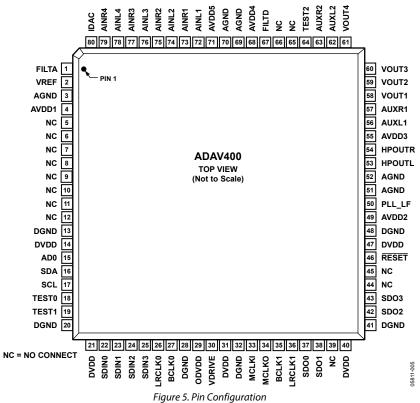

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

| Pin No.                      | Mnemonic   | I/O | Description                                                                                                                                                                            |

|------------------------------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                            | FILTA      | 0   | ADC Filter Decoupling Node for the ADC. Decouple this pin to AGND (Pin 3).                                                                                                             |

| 2                            | VREF       |     | Voltage Reference. This pin is driven by an internal 1.5 V reference voltage. Decouple this pin to AGND (Pin 3).                                                                       |

| 3                            | AGND       |     | ADC Ground. Connect this pin to the analog ground plane.                                                                                                                               |

| 4                            | AVDD1      |     | Analog Power Supply Pin for the ADC. Connect this pin to 3.3 V and decouple to AGND (Pin 3).                                                                                           |

| 5 to 12,<br>65, 66           | NC         |     | Not Connected Internally.                                                                                                                                                              |

| 13, 20,<br>28, 32,<br>41, 48 | DGND       |     | Digital Ground. Connect this pin to the digital ground plane.                                                                                                                          |

| 14, 21,<br>31, 40,<br>47     | DVDD       |     | Digital Power Supply Pins. Connect these pins to 1.8 V, either directly or by using the on-chip regulator. Decouple to DGND.                                                           |

| 15                           | AD0        | I   | I <sup>2</sup> C Address Select. Tie to ODVDD for Address 0x28 (write) and Address 0x29 (read) or to DGND for Address 0x2A (write) and Address 0x2B (read).                            |

| 16                           | SDA        | I/O | Serial Data Input/Output for the I <sup>2</sup> C Control Port.                                                                                                                        |

| 17                           | SCL        | I   | Serial Clock for the I <sup>2</sup> C Control Port.                                                                                                                                    |

| 18                           | TEST0      |     | Test Pin. Connect to ODVDD.                                                                                                                                                            |

| 19                           | TEST1      |     | Test Pin. Connect to ODVDD.                                                                                                                                                            |

| 22 to 25                     | SDIN [0:3] | Ι   | Serial Data Inputs. BCLK1 and LRCLK1 are used as the timing signals for SDIN0 to SDIN3.                                                                                                |

| 26                           | LRCLK0     | I   | Left/Right Clock for Sample Rate Converter (SRC). This input frame synchronization signal is associated with SDIN0 to SDIN3 when one of these input channels is redirected to the SRC. |

| 27                           | BCLK0      | 1   | Bit Clock for Sample Rate Converter (SRC). This input clock is associated with SDIN0 to SDIN3 when one of these input channels is redirected to the SRC.                               |

| 29                           | ODVDD      |     | Digital Interface Supply (3.3 V) Pin. Connect this pin to a 3.3 V digital supply. Decouple to DGND.                                                                                    |

| 30                           | VDRIVE     |     | Drive for External PNP Transistor. This is used with the on-chip 1.8 V regulator circuit.                                                                                              |

| Pin No.           | Mnemonic   | I/O | Description                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33                | MCLKI      | Ι   | Master Clock Input. The ADAV400 uses a phase-locked loop (PLL) to generate the appropriate internal clock for the DSP core.                                                                                                                                                                                                                                                     |

| 34                | MCLKO      | 0   | Audio Clock Output. The MCLKO pin can be programmed to output the internal audio clock.                                                                                                                                                                                                                                                                                         |

| 35                | BCLK1      | I/O | Bit Clock for Serial Data Input/Output. This clock and the LRCLK1 are used as clock and frame sync signals for the SDINx and SDOx pins. These clocks are inputs to the ADAV400 when the port is configured as a slave, and outputs when the port is configured as a master. On power up, these pins are set to slave mode to avoid conflicts with external master mode devices. |

| 36                | LRCLK1     | I/O | Left/Right Clock for Serial Data Input/Output. This clock and the BCLK1 are used as clock and frame sync signals for the SDINx and SDOx pins.                                                                                                                                                                                                                                   |

| 37, 38,<br>42, 43 | SDO [0:3]  | 0   | Serial Data Outputs.                                                                                                                                                                                                                                                                                                                                                            |

| 39, 44,<br>45     | NC         |     | These pins should be left unconnected.                                                                                                                                                                                                                                                                                                                                          |

| 46                | RESET      | Ι   | Active Low Reset Signal. After RESET the ADAV400 is powered down.                                                                                                                                                                                                                                                                                                               |

| 49                | AVDD2      |     | Analog Power Supply Pin for the PLL. Connect this pin to 3.3 V and decouple to AGND (Pin 51).                                                                                                                                                                                                                                                                                   |

| 50                | PLL_LF     |     | PLL Loop Filter. External components are required to allow the PLL to function correctly. See the PLL Block section for details of these components.                                                                                                                                                                                                                            |

| 51                | AGND       |     | PLL Ground. Connect this pin to the analog ground plane.                                                                                                                                                                                                                                                                                                                        |

| 52                | AGND       |     | Headphone Driver Ground. Connect this pin to the analog ground plane.                                                                                                                                                                                                                                                                                                           |

| 53                | HPOUTL     | 0   | Left Headphone Output. Analog output from the headphone amplifiers.                                                                                                                                                                                                                                                                                                             |

| 54                | HPOUTR     | 0   | Right Headphone Output. Analog output from the headphone amplifiers.                                                                                                                                                                                                                                                                                                            |

| 55                | AVDD3      |     | Analog Power Supply Pin for the Headphone Amplifier. Connect this pin to 3.3 V and decouple to AGND (Pin 52).                                                                                                                                                                                                                                                                   |

| 56                | AUXL1      | 0   | Auxiliary Analog Output Left 1.                                                                                                                                                                                                                                                                                                                                                 |

| 57                | AUXR1      | 0   | Auxiliary Analog Output Right 1.                                                                                                                                                                                                                                                                                                                                                |

| 58 to 61          | VOUT [1:4] | 0   | Main Analog Output 1 to Output 4.                                                                                                                                                                                                                                                                                                                                               |

| 62                | AUXL2      | 0   | Auxiliary Analog Output Left 2.                                                                                                                                                                                                                                                                                                                                                 |

| 63                | AUXR2      | 0   | Auxiliary Analog Output Right 2.                                                                                                                                                                                                                                                                                                                                                |

| 64                | TEST2      |     | Test Pin. This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                                  |

| 67                | FILTD      |     | DAC Filter Decoupling Node. Decouple this pin to AGND (Pin 69).                                                                                                                                                                                                                                                                                                                 |

| 68                | AVDD4      |     | Analog Power Supply Pin for the DAC. Connect this pin to 3.3 V and decouple to AGND (Pin 69).                                                                                                                                                                                                                                                                                   |

| 69, 70            | AGND       |     | DAC Ground. Connect this pin to the analog ground plane.                                                                                                                                                                                                                                                                                                                        |

| 71                | AVDD5      |     | Analog Power Supply Pin for the DAC. Connect this pin to 3.3 V and decouple to AGND (Pin 70).                                                                                                                                                                                                                                                                                   |

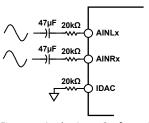

| 72, 74,<br>76, 78 | AINL [1:4] |     | Left Analog Input 1 to Input 4. The analog inputs are current inputs typically driven via a 20 k $\Omega$ resistor for 2 V rms input, as shown in Figure 17.                                                                                                                                                                                                                    |

| 73, 75,<br>77, 79 | AINR [1:4] | Ι   | Right Analog Input 1 to Input 4. The analog inputs are current inputs typically driven via a 20 k $\Omega$ resistor for 2 V rms input, as shown in Figure 17.                                                                                                                                                                                                                   |

| 80                | IDAC       |     | DAC External Bias Resistor. This is an external bias pin for the DAC circuitry. Connect a 20 k $\!\Omega$ resistor between this pin and AGND.                                                                                                                                                                                                                                   |

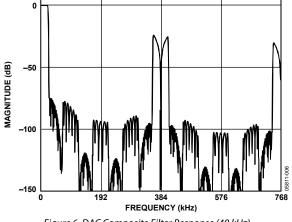

# **TYPICAL PERFORMANCE CHARACTERISTICS**

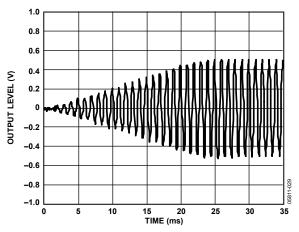

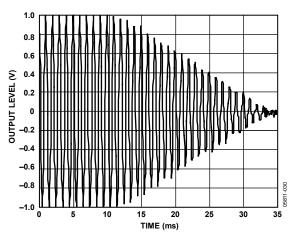

Figure 15. ADC Total Harmonic Distortion + Noise

## THEORY OF OPERATION

The ADAV400 is an enhanced audio processor containing an Analog Devices SigmaDSP digital processing core. The core can accept up to four digital stereo channels, typically at 48 kHz, or three channels, typically at 48 kHz, and one channel at any sample rate between 5 kHz and 50 kHz. In addition, up to four stereo analog inputs can be used as the source for the DSP core using the stereo ADC and a four-stereo input mux.

Outputs from the DSP core are available as four stereo digital outputs and four stereo analog outputs.

The core of the ADAV400 is a 28-bit DSP (56-bit with double precision) optimized for audio processing. Signal processing parameters are stored in a 1024-location parameter RAM. The program RAM can be loaded with a custom program after power-up. New values are written to the program and parameter RAM using the I<sup>2</sup>C control port. The values stored in the parameter RAM control individual signal processing blocks, such as IIR equalization filters, dynamics processors, audio delays, and mixer levels. A safe load feature allows transparent updating of these parameters, eliminating the risk of unwanted pops or clicks in the outputs.

The ADAV400 has a sophisticated control port that supports complete read/write capability of all memory locations except the target/slew RAM and data RAM, which are only accessible by the DSP core.

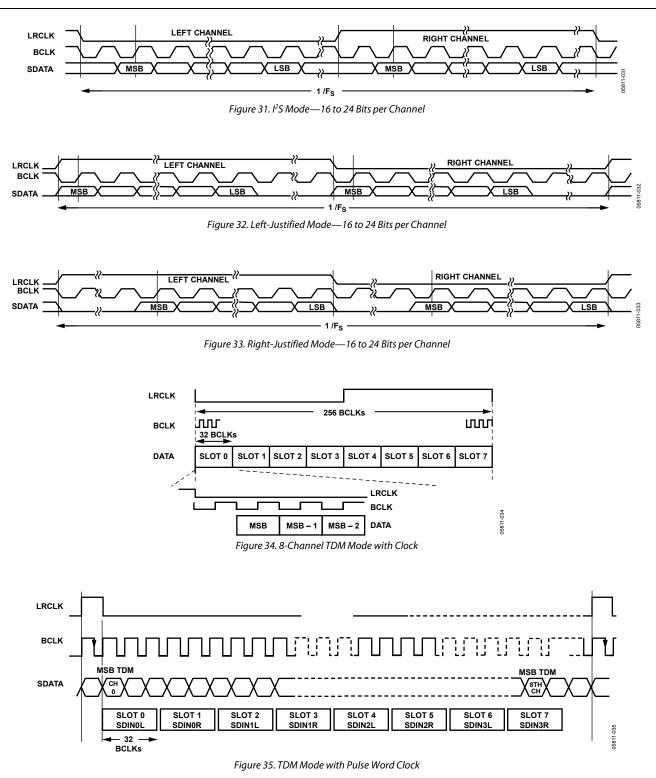

The ADAV400 has a very flexible serial data input and output port that allows for glueless interconnection to a variety of ADCs, DACs, general-purpose DSPs, S/PDIF receivers, and sample rate converters. The digital inputs and outputs of the ADAV400 can be configured in I<sup>2</sup>S, left-justified, right-justified, or TDM serial port–compatible mode. They can support 16, 20, or 24 bits in all modes. The ADAV400 accepts serial audio data in MSB-first and twos complement formats.

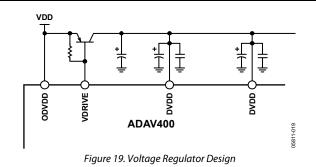

The digital core of the ADAV400 operates at 1.8 V, and the other circuit blocks operate from a 3.3 V power supply. An on-board regulator allows a single 3.3 V supply for both digital supplies using the configuration shown in Figure 19.

The ADAV400 is fabricated on a single monolithic integrated circuit and is housed in an 80-lead LQFP for operation over the 0°C to 70°C consumer temperature range.

### **ANALOG INPUTS**

The ADAV400 has four stereo analog inputs. An input multiplexer is included that enables any of these four stereo analog inputs to be connected to the ADC. The analog inputs are current inputs; see Figure 17 for the suggested input configuration when the required input level is 2 V rms.

Figure 17. Analog Input Configuration

05811-016

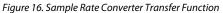

### SAMPLE RATE CONVERTER BLOCK

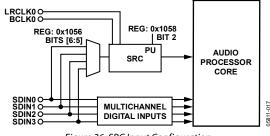

The ADAV400 contains a stereo SRC that accepts input sample rates in the range of 5 kHz to 50 kHz. Any one of the digital inputs can be selected as the source for the SRC.

Note that the SRC has a filter cutoff frequency of 20 kHz for a 48 kHz sample rate. If a different input sample rate is used, the cutoff frequency scales accordingly.

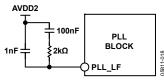

### **PLL BLOCK**

The ADAV400 contains a phase-locked loop (PLL) that generates all of the internal clocks required by the ADAV400. The master clock frequency can be  $64 \times f_s$ ,  $128 \times f_s$ ,  $256 \times f_s$ , or  $512 \times f_s$ .

The PLL requires some external components to operate correctly, as shown in Figure 18. These components form a loop filter that integrates pulses from a charge pump and produces a voltage to tune the VCO. Internally, the PLL can generate clocks of up to 200 MHz, so it is recommended that a suitable capacitor be selected.

Figure 18. PLL Loop Filter Components

A 3.3 V analog supply connected to AVDD2 is required to operate the PLL. Where the supply for AVDD1 is also used for the PLL, additional filtering is recommended to prevent digital noise created by the PLL block being coupled to the analog circuitry powered by the AVDD1 supply.

#### **ANALOG OUTPUTS**

The ADAV400 contains four stereo analog outputs typically at 1 V rms. One stereo pair of DACs is connected to integrated headphone amplifiers HPOUTL and HPOUTR, but is also available on the AUXL1 and AUXR1 pins.

Note that the outputs of all the DACs are inverted with the exception of the headphone channel. If required, this can be changed using the invert library block of the DSP.

### **HEADPHONE AMPLIFIER**

The ADAV400 has an integrated stereo headphone amplifier capable of driving 32 mW into a 32  $\Omega$  load.

### **VOLTAGE REGULATOR**

The ADAV400 includes an on-chip voltage regulator that enables the chip to be used in systems where a 1.8 V supply is not available. The only external components needed are a PNP transistor (such as FZT953), a single capacitor, and a single resistor. The recommended design for the voltage regulator is shown in Figure 19.

As shown in this figure, VDD is the main system voltage (3.3 V). A voltage of 1.8 V is generated at the transistor's collector and is connected to the DVDD pins. VDRIVE is an output from the internal regulator circuit on the ADAV400 and is connected to the base of the PNP transistor.

There are two specifications to take into consideration when choosing the regulator's transistor. First,  $h_{FE}$  should be at least 100. Second, the collector power dissipation,  $P_c$ , must be greater than

$P_C = (3.3 \text{ V} - 1.8 \text{ V}) \times 135 \text{ mA} = 202.5 \text{ mW}$

### **CONTROL PORT**

The ADAV400 control port has full read and write capability to all registers and RAMs with the exception of the data RAM, which is only accessible by the DSP core. Single or burst mode reads and writes are supported. A typical word consists of the chip address, the register or RAM subaddress, and the data to be written. The number of bytes per data-word depends on the address of the location being written to or read from.

The first byte of a control word (Byte 0) contains the 7-bit chip address plus the  $R/\overline{W}$  bit. The next two bytes (Byte 1 and Byte 2) together form the subaddress of the memory or register location within the ADAV400. All subsequent bytes contain data that can be writes to the control register or updates to the program and parameter memories. Table 16 to Table 25 provide more details on the I<sup>2</sup>C write and read formats.

The ADAV400 has several mechanisms for updating signal processing parameters in real time without causing pops or clicks. In cases where large blocks of data need to be transferred, it is recommended to mute the output of the DSP core by setting Bit 9 of the audio core control register to 0, and then load the new data and set Bit 9 back to 1. This is typically done during the booting sequence at startup or when loading a new program into RAM.

In cases where only a few parameters need to be changed—for example, updating a biquad—the new parameters can be loaded without halting the program. To avoid unwanted pops or clicks in the output during the loading sequence, the DSP core uses an internal safe load mechanism that buffers the data and only updates the parameter memory at the end of the sample period and before the start of the next sample period.

### I<sup>2</sup>C PORT

The ADAV400 supports a 2-wire serial (I<sup>2</sup>C-compatible) microprocessor bus driving multiple peripherals. Two pins, serial data (SDA) and serial clock (SCL), carry information between the ADAV400 and the system I<sup>2</sup>C master controller. The ADAV400 is always a slave on the I<sup>2</sup>C bus, which means that it never initiates a data transfer. Each slave device is recognized by a unique address.

The ADAV400 has four possible slave addresses, two for writing operations and two for reading operations. These are unique addresses for the device and are illustrated in Table 5. The LSB of the byte sets either a read or a write operation; Logic Level 1 corresponds to a read operation, and Logic Level 0 corresponds to a write operation. The seventh bit of the address is set by tying the AD0 pin of the ADAV400 to Logic Level 0 or Logic Level 1.

| Tuble 5.1 C Hudresses |     |               |  |  |  |  |

|-----------------------|-----|---------------|--|--|--|--|

| AD0                   | R/W | Slave Address |  |  |  |  |

| 0                     | 0   | 0x28          |  |  |  |  |

| 0                     | 1   | 0x29          |  |  |  |  |

| 1                     | 0   | 0x2A          |  |  |  |  |

| 1                     | 1   | 0x2B          |  |  |  |  |

### Addressing

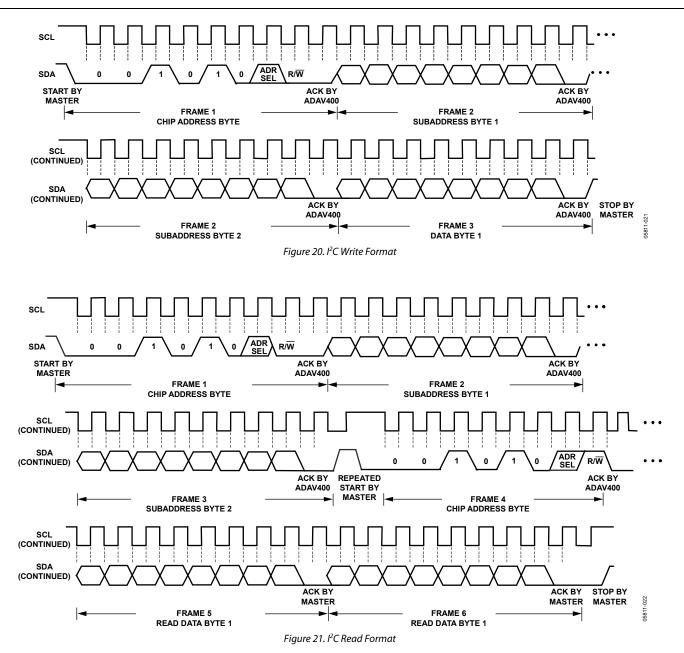

Initially, all devices on the I<sup>2</sup>C bus are in an idle state, wherein the devices monitor the SDA and SCL lines for a start condition and the proper address. The I<sup>2</sup>C master initiates a data transfer by establishing a start condition, defined by a high-to-low transition on SDA while SCL remains high. This indicates that an address/data stream follows. All devices on the bus respond to the start condition and read the next byte (7-bit address +  $R/\overline{W}$  bit) MSB first. The device that recognizes the transmitted address responds by pulling the data line low during the ninth clock pulse. This ninth bit is known as an acknowledge bit. All other devices on the bus revert to an idle condition. The  $R/\overline{W}$ bit determines the direction of the data. A Logic Level 0 on the LSB of the first byte means the master writes information to the peripheral. A Logic Level 1 on the LSB of the first byte means the master reads information from the peripheral. A data transfer takes place until a stop condition is encountered. A stop condition occurs when SDA transitions from low to high while SCL is held high. Figure 20 shows the timing of an I<sup>2</sup>C write.

Burst mode addressing, where the subaddresses are automatically incremented at word boundaries, can be used for writing large amounts of data to contiguous memory locations. This increment happens automatically if a stop condition is not encountered after a single word write. A data transfer is always terminated by a stop condition.

Stop and start conditions can be detected at any stage during the data transfer. If these conditions are asserted out of sequence with normal read and write operations, it causes an immediate jump to the idle condition. During a given SCL high period, the user should only issue one start condition, one stop condition, or a single stop condition followed by a single start condition. If an invalid subaddress is issued by the user, the ADAV400 does not issue an acknowledge and reverts to an idle state. If the user exceeds the highest subaddress while in autoincrement mode, one of two actions is taken. In read mode, the ADAV400 outputs the highest subaddress register contents until the master device issues a no acknowledge, indicating the end of a read. A no acknowledge condition is where the SDA line is not pulled low on the ninth clock pulse on SCL. If the highest subaddress location is reached while in write mode, the data for the invalid byte is not loaded into any subaddress register, a no acknowledge is issued by the ADAV400, and the part returns to the idle condition.

#### I<sup>2</sup>C Read and Write Operations

Table 6 shows the timing of a single word write operation. Every ninth clock, the ADAV400 issues an acknowledge by pulling SDA low.

Table 7 shows the timing of a burst mode write sequence. This table shows an example where the target destination registers are two bytes. The ADAV400 auto-increments its subaddress register counter every two bytes until a stop condition occurs.

The timing of a single word read operation is shown in Table 8. Note that the first R/W bit is still a 0, indicating a write operation. This is because the subaddress must be written to set up the internal address. After the ADAV400 acknowledges the receipt of the subaddress, the master must issue a repeated start command

followed by the chip address byte with the  $R/\overline{W}$  set to 1 (read). The ADAV400 responds with the read result on SDA. The master then responds every ninth clock with an acknowledge pulse to the ADAV400.

Table 9 shows the timing of a burst mode read sequence. This table shows an example where the target read registers are two bytes. The ADAV400 increments its subaddress register every two bytes because the requested subaddress corresponds to a register or memory area with word lengths of two bytes. Other address ranges may have a variety of word lengths ranging from one to six bytes; the ADAV400 always decodes the subaddress and sets the auto-increment circuit so that the address increments after the appropriate number of bytes.

#### Key for Table 6 to Table 9

S = start bit P = stop bit AM = acknowledge by master AS = acknowledge by slave

#### Table 6. Single Word I<sup>2</sup>C Write

|   | 0                                |    |                 |    |                |    |             |    |             |        |             |   |

|---|----------------------------------|----|-----------------|----|----------------|----|-------------|----|-------------|--------|-------------|---|

| S | Ch <u>ip</u> address,<br>R/W = 0 | AS | Subaddress high | AS | Subaddress low | AS | Data Byte 1 | AS | Data Byte 2 | <br>AS | Data Byte N | Р |

#### Table 7. Burst Mode I<sup>2</sup>C Write

| S | Chip     | AS | Subaddress | AS | Subaddress | AS | Data-Word 1, | AS | Data-Word 1, | AS | Data-Word 2, | AS | Data-Word 2, | AS | <br>Р |

|---|----------|----|------------|----|------------|----|--------------|----|--------------|----|--------------|----|--------------|----|-------|

|   | address, |    | high       |    | low        |    | Byte 1       |    | Byte 2       |    | Byte 1       |    | Byte 2       |    |       |

|   | R/W = 0  |    |            |    |            |    |              |    |              |    |              |    |              |    |       |

#### Table 8. Single Word I<sup>2</sup>C Read

|   | 0                        |    |                    |    |                   |    |   |                          |    |             |    |                |        |                |   |

|---|--------------------------|----|--------------------|----|-------------------|----|---|--------------------------|----|-------------|----|----------------|--------|----------------|---|

| S | Chip address,<br>R/W = 0 | AS | Subaddress<br>high | AS | Subaddress<br>low | AS | S | Chip address,<br>R/W = 1 | AS | Data Byte 1 | AM | Data<br>Byte 2 | <br>AM | Data<br>Byte N | Р |

#### Table 9. Burst Mode I<sup>2</sup>C Read

| S | Ch <u>ip</u> address,<br>R/W = 0 | AS | Subaddress<br>high | AS | Subaddress<br>low | AS | S | Ch <u>ip</u> address,<br>R/W = 1 | AS | Data-Word 1<br>Byte 1 | AM | Data-Word 1<br>Byte 2 | AM |  | Ρ |

|---|----------------------------------|----|--------------------|----|-------------------|----|---|----------------------------------|----|-----------------------|----|-----------------------|----|--|---|

|---|----------------------------------|----|--------------------|----|-------------------|----|---|----------------------------------|----|-----------------------|----|-----------------------|----|--|---|

# **SIGNAL PROCESSING**

The ADAV400 is designed to provide all the signal processing functions commonly used in stereo or multichannel playback systems. The signal processing flow is created using a graphical development tool supplied by Analog Devices, which allows fast development of even complex audio flows and real-time control of all signal processing functions.

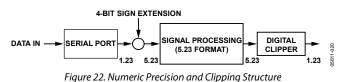

The input and output word lengths are 24 bits. Four extra headroom bits are used in the processor to allow internal gains of up to 24 dB without clipping.

The signal processing blocks can be arranged in a custom program that is loaded to the RAM of the ADAV400. The available signal processing blocks are outlined in the Numeric Formats and Programming sections.

### NUMERIC FORMATS

It is common in DSP systems to use a standardized method of specifying numeric formats. Fractional number systems are specified by an A.B format, where A is the number of bits to the left of the decimal point and B is the number of bits to the right of the decimal point.

The ADAV400 uses the same numeric format for both the coefficient values (stored in the parameter RAM) and the signal data values.

#### Numeric Format: 5.23

#### Range

-16.0 to (+16.0 - 1 LSB)

#### Examples

$\begin{aligned} &1000\ 0000\ 0000\ 0000\ 0000\ 0000\ = -16.0\\ &1110\ 0000\ 0000\ 0000\ 0000\ 0000\ = -4.0\\ &1111\ 1000\ 0000\ 0000\ 0000\ 0000\ 0000\ = -1.0\\ &1111\ 1110\ 0000\ 0000\ 0000\ 0000\ 0000\ = -0.25\\ &1111\ 1111\ 1111\ 1111\ 1111\ 1111\ = (1\ LSB\ below\ 0.0)\\ &0000\ 0000\ 0000\ 0000\ 0000\ 0000\ = -0.25\\ &0000\ 0010\ 0000\ 0000\ 0000\ 0000\ 0000\ = -0.25\\ &0000\ 1000\ 0000\ 0000\ 0000\ 0000\ 0000\ = +1.0\\ &0010\ 0000\ 0000\ 0000\ 0000\ 0000\ = +4.0\\ &0111\ 1111\ 1111\ 1111\ 1111\ 1111\ 1111\ 1111\ = (+16.0\ -1\ LSB)\end{aligned}$

The serial port accepts up to 24 bits on the input and is signextended to the full 28 bits of the core. This allows internal gains of up to 24 dB without encountering internal clipping. A digital clipper circuit is used between the output of the DSP core and the serial output ports (see Figure 22). This clips the top four bits of the signal to produce a 24-bit output with a range of +1.0 (-1 LSB) to -1.0.

### PROGRAMMING

On power-up, the default program of the ADAV400 passes the unprocessed input signals to the outputs, but the outputs are muted by default. There are 2560 instruction cycles per audio sample. This DSP runs in a stream-oriented manner, meaning all 2560 instructions are executed each sample period. The ADAV400 can also be set up to accept double- or quad-speed inputs by reducing the number of instructions per sample. This is set in the audio core control register.

The part is easily programmed using graphical tools provided by Analog Devices. No knowledge of DSP assembly code is required to program the ADAV400. Simply connect graphical blocks, such as biquad filters, dynamics processors, mixers, and delays, in a signal flow schematic. The schematic is then compiled, and the program and parameter files are loaded into the program RAM of the ADAV400 through the control port. Signal processing blocks available in the provided libraries include

- Single- and double-precision biquad filters

- Monochannel and multichannel dynamics processors

- Mixers and splitters

- Tone and noise generators

- First-order filters

- Fixed and variable gain

- RMS look-up tables

- Loudness

- Delay

- Stereo enhancement (Phat Stereo<sup>™</sup>)

- Dynamic bass boost

- Interpolators and decimators

Additional blocks are always in development. Analog Devices also provides proprietary and third-party algorithms for applications such as matrix decoding, bass enhancement, and surround virtualizers. Contact Analog Devices for information about licensing these algorithms.

## RAMS AND REGISTERS

**Table 10. Control Port Addresses**

| I <sup>2</sup> C Subaddress     | Register Name                                           | Read/Write Word Length        |

|---------------------------------|---------------------------------------------------------|-------------------------------|

| 0 to 1023 (0x0000 to 0x03FF)    | Parameter RAM                                           | Write: 4 bytes; read: 4 bytes |

| 1024 to 3584 (0x0400 to 0x0E00) | Program RAM                                             | Write: 6 bytes; read: 6 bytes |

| 4096 to 4159 (0x1000 to 0x103F) | Target/slew RAM                                         | Write: 5 bytes; read: N/A     |

| 4160 to 4164 (0x1040 to 0x1044) | Parameter RAM Data Safe Load Register [0:4]             | Write: 5 bytes; read: N/A     |

| 4165 to 4169 (0x1045 to 0x1049) | Parameter RAM Indirect Address Safe Load Register [0:4] | Write: 2 bytes; read: N/A     |

| 4170 to 4175 (0x104A to 0x104F) | Data Capture Register [0:5] (control port readback)     | Write: 2 bytes; read: 3 bytes |

| 4176 to 4177 (0x1050 to 0x1051) | Data capture registers (digital output)                 | Write: 2 bytes; read: N/A     |

| 4178 (0x1052)                   | Audio core control register                             | Write: 2 bytes; read: 2 bytes |

| 4179 (0x1053)                   | RAM modulo control register                             | Write: 1 byte; read: 1 byte   |

| 4180 (0x1054)                   | Serial output control register                          | Write: 2 bytes; read: 2 bytes |

| 4181 (0x1055)                   | Serial input control register                           | Write: 1 byte; read: 1 byte   |

| 4182 (0x1056)                   | SRC serial port control register                        | Write: 1 byte; read: 1 byte   |

| 4183 (0x1057)                   | ADC input mux control register                          | Write: 2 bytes; read: 2 bytes |

| 4184 (0x1058)                   | Power control register                                  | Write: 2 bytes; read: 2 bytes |

| 4185 (0x1059)                   | User Control 1 register                                 | Write: 2 bytes; read: 2 bytes |

| 4186 (0x105A)                   | User Control 2 register                                 | Write: 2 bytes; read: 2 bytes |

| 4365 (0x110D)                   | DAC amplifier register                                  | Write: 2 bytes; read: 2 bytes |

#### Table 11. RAM Read/Write Modes

| Memory          | Size      | Subaddress Range                   | Read | Write | Burst Mode Available | Write Modes                                |

|-----------------|-----------|------------------------------------|------|-------|----------------------|--------------------------------------------|

| Parameter RAM   | 1024 × 28 | 0 to 1023<br>(0x0000 to 0x03FF)    | Yes  | Yes   | Yes                  | Direct write, <sup>1</sup> safe load write |

| Program RAM     | 2560 × 42 | 1024 to 3584<br>(0x0400 to 0x0E00) | Yes  | Yes   | Yes                  | Direct write <sup>1</sup>                  |

| Target/Slew RAM | 64 × 34   | 4096 to 4159<br>(0x1000 to 0x1044) | No   | Yes   | No                   | Safe load write                            |

<sup>1</sup> To avoid clicks or pops, mute the DSP core first.

### **CONTROL PORT ADDRESSING**

Table 10 shows the addressing of the RAM and register spaces on the ADAV400. The address space encompasses a set of registers and three RAMs: parameter, program, and target/slew. Table 11 lists the sizes and available writing modes of the parameter, program, and target/slew RAMs.

#### PARAMETER RAM CONTENTS

The parameter RAM is 28 bits wide and occupies Address 0 to Address 1023. The parameter RAM is initialized to all 0s on power-up. The data format of the parameter RAM is twos complement 5.23. This means that the coefficients can range from +16.0 (-1 LSB) to -16.0, with 1.0 represented by the binary word 0000 1000 0000 0000 0000 0000.

#### **Options for Parameter Updates**

The parameter RAM can be written to and read from using one of the two following methods:

• Direct Read/Write.

This method allows direct access to the program and parameter RAMs. It is normally used during a complete new load of the RAMs using burst mode addressing. To avoid clicks or pops in the outputs, it is recommended to set the clear registers bit in the audio core control register to 0.

• Safe Load Write.

Up to five safe load registers can be loaded with parameter RAM address data. The data is transferred to the requested address when the RAM is idle. It is recommended to use this method for dynamic updates during run time. For example, a complete update of one biquad section can occur in one audio frame. This method is not available for writing to the program RAM or control registers. The following sections discuss these two options in more detail.

### RECOMMENDED PROGRAM/PARAMETER LOADING PROCEDURES

When writing large amounts of data to the program or parameter RAM in direct write mode, disable the processor core to prevent pops or clicks in the audio output. The ADAV400 contains several mechanisms for disabling the core.

If the loaded program does not use the target/slew RAM as the main system volume control (for example, the default power-up program),

- 1. Assert Bit 9 (low to assert—default setting) and Bit 6 (high to assert) of the audio core control register. This clears the accumulators, the serial output registers, and the serial input registers.

- 2. Fill the program RAM using burst mode writes.

- 3. Fill the parameter RAM using burst mode writes.

- Assert Bit 7 of the audio core control register to initiate a data memory clear sequence. Wait at least 100 μs for this sequence to complete. This bit is automatically cleared after the operation is complete.

- 5. Deassert Bit 9 and Bit 6 of the audio core control register to allow the core to begin normal operation

If the loaded program does use the target/slew RAM as the main system volume control,

- 1. Assert Bit 12 of the audio core control register. This begins a volume ramp-down, with a time constant determined by the upper bits of the target RAM. Wait for this ramp-down to complete (the user can poll Bit 13 of the audio core control register, or simply wait for a given amount of time).

- 2. Assert Bit 9 (low to assert) and Bit 6 (high to assert) of the audio core control register. This clears the accumulators, the serial output registers, and the serial input registers.

- 3. Fill the program RAM using burst mode writes.

- 4. Fill the parameter RAM using burst mode writes.

- 5. Assert Bit 7 of the audio core control register to initiate a data memory clear sequence. Wait at least  $100 \ \mu s$  for this sequence to complete. This bit is automatically cleared after the operation is complete.

- 6. Deassert Bit 9 and Bit 6 of the audio core control register.

- 7. If the newly loaded program also uses the target/slew RAM, deassert Bit 12 of the audio core control register to begin a volume ramp-up procedure.

#### TARGET/SLEW RAM

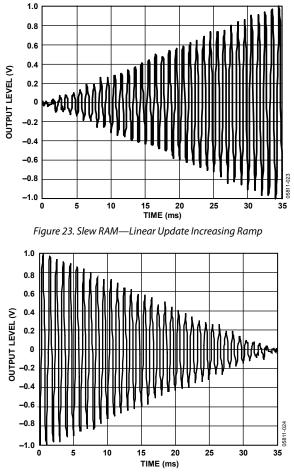

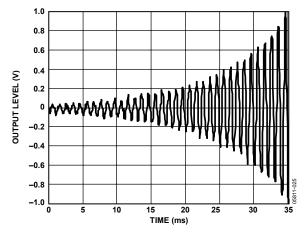

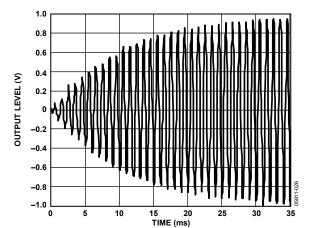

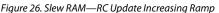

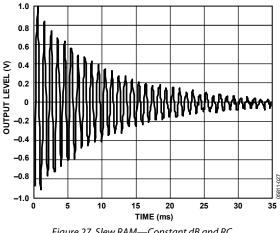

The target/slew RAM is a bank of 64 RAM locations, each of which can be set to autoramp from one value to a desired final value in one of four modes.

When a program is loaded into the program RAM using one or more locations in the slew RAM to access internal coefficient data, the target/slew RAM is used by the DSP. Typically, these coefficients are used for volume controls or smooth cross-fading effects, but they can also be used to update any value in the parameter RAM. Each of the 64 locations in the slew RAM is linked to a corresponding location in the target RAM. When a new value is written to the target RAM using the control port, the corresponding slew RAM location begins to ramp toward the target. The value is updated once per audio frame (LRCLK period).

The target RAM is 34 bits wide. The lower 28 bits contain the target data in 5.23 format for the linear and exponential (constant dB and RC) ramp types. For constant time ramping, the lower 28 bits contain 16 bits in 2.14 format and 12 bits to set the current step. The upper six bits are used to determine the type and speed of the ramp envelope in all modes. The format of the data write for linear and exponential formats is shown in Table 12. Table 13 shows the data write format for the constant time ramping.

In normal operation, write data to the target/slew RAM using the safe load registers as described in the Safe Load Registers section. A mute slew RAM bit is included in the audio core control register to simultaneously set all the slew RAM target values to 0. This is useful for implementing a global multichannel mute. When this bit is deasserted, all slew RAM values return to their original premuted states.

#### Table 12. Linear, Constant dB, and RC Ramp Data Write

| Byte 0           | Byte 1            | Bytes [2:4] |

|------------------|-------------------|-------------|

| 000000,          | time_const [3:0], | data [23:0] |

| curve_type [1:0] | data [27:24]      |             |

#### Table 13. Constant Time Ramp Data Write

| Byte 0           | Byte 1                         | Bytes [2:4]     |  |  |

|------------------|--------------------------------|-----------------|--|--|

| 000000,          | update_step [0],               | data [11:0],    |  |  |

| curve_type [1:0] | #_of_steps [2:0], data [15:12] | reserved [11:0] |  |  |

There are four types of ramping curves:

• Linear.

The value slews to the target value using a fixed step size.

• Constant dB.

The value slews to the target value using the current value to calculate the step size. The resulting curve has a constant rise and decay when measured in decibels.

• RC.

The value slews to the target value using the difference between the target and current values to calculate the step size, resulting in a simple RC response.

• Constant Time.

The value slews to the target value in a fixed number of steps in a linear fashion. The control port mute has no effect on this type of ramping curve.

| Settings | Ramp Type     |

|----------|---------------|

| 00       | Linear        |

| 01       | Constant dB   |

| 10       | RC            |

| 11       | Constant time |

The following sections detail how the control port writes to the target/slew RAM to control the time constant and ramp type parameters.

#### Ramp Types [1:3]—Linear, Constant dB, RC (34-Bit Write)

The target word for the first three ramp types is broken into three parts. The 34-bit command is written with six leading 0s to extend the data write to five bytes. The parts of the target RAM write are

- Ramp type (two bits).

- Time constant (four bits).

- 0000 = fastest

- 1111 =slowest

- Data (28 bits): 5.23 format.

### Ramp Type 4—Constant Time (34-Bit Write)

The target word for the constant time ramp type is written in five parts, with the 34-bit command written with six leading 0s to extend the data write to five bytes. The parts of the constant time target RAM write are

- Ramp type (two bits).

- Update step (one bit). Set to 1 when a new target is loaded to trigger a step value update. The value is automatically reset after the step value is updated.